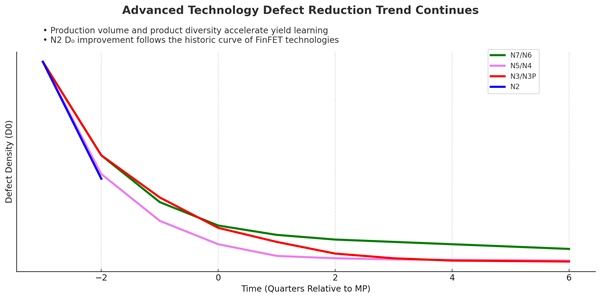

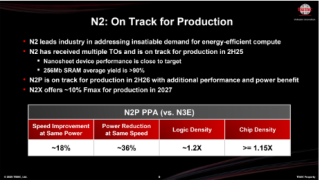

台积电公布了其最新的N2 2nm制程的缺陷率数据,表明其性能表现优异,相较于先前的3nm、5nm和7nm制程,缺陷率更低,这一突破性的技术进展有望为高性能计算和人工智能领域带来更大的性能提升和能效优化,台积电在制程技术领域的持续创新,进一步巩固了其作为全球领先的半导体制造企业的地位。

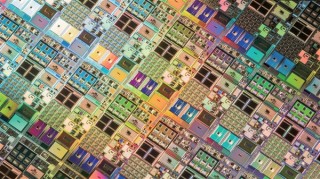

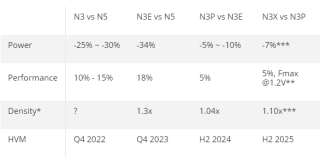

电脑知识网报道,于近期北美技术论坛上,台积电首度公开了其N2 2nm工艺的缺陷率(D0)情况,令人振奋的是,相较于历史上的7nm、5nm、3nm工艺,N2工艺的缺陷率表现更为出色。 台积电并未透露具体的缺陷率数据,而是呈现了各工艺随时间变化的缺陷率趋势,值得注意的是,台积电的N2工艺首次引入了GAAFET全环绕晶体管技术,尽管距离大规模量产还有两季度,也就是预计要到年底,但从目前试产的情况来看,前景相当乐观。 红色标注的关键信息指出,N2工艺在近两个月的试产中,其缺陷率与同期的N5/N4相当,甚至略低,明显优于N7/N6、N3/N3P,在试产到量产的半年的时间周期内,N7/N6的综合缺陷率最高,相较之下,N3/N3P从量产开始就表现出较低的缺陷率,而N5/N4的情况更佳,从试产阶段就展现出较低的缺陷率,若N2能够延续N5/N4的这一趋势,无疑将会在未来市场大放异彩。 台积电强调,一种工艺的缺陷率能否迅速降低,不仅取决于设计和技术本身,还受到制造芯片的数量和产能规模的影响,大规模的芯片制造有助于更轻易地察觉缺陷并作出改进,台积电的N2工艺已流片的芯片数量明显更多,这也是其能够快速降低缺陷率的重要原因之一。 台积电在N2 2nm工艺的研发上取得了显著的进展,其引入的全新技术和优秀的缺陷率表现令人期待,我们拭目以待,期待其在年底的大规模量产中继续展现出色的表现,以上信息图片已居中并添加黑色1px的实线边框。